ソフトスイッチング概観

私がパワーエレクトロニクス研究室に配属されて、最も理解が困難だったのがzero volt switching (ZVS)およびソフトスイッチングでした。ZVS動作で代表的なDABコンバータの関連論文で学位を取得しましたが、今でも完全に半導体のスイッチング動作を理解しているかと問われると疑問符が付きます。そこで本記事に2024年現在までの、パワー半導体デバイス、特にMOSFETのソフトスイッチングに関する自身の理解を記録しておこうと思います。間違っていたらぜひ指摘してください。

電気学会による定義と電圧-電流平面におけるスイッチング動作

電気学会の電気専門用語集では、ソフトスイッチングの定義を以下の文言で定義しています。

スイッチング過程における半導体バルブデバイスの電圧-電流平面上の軌跡が最大電圧点、最大電流点および原点を結ぶ三角形の領域内で動くスイッチング動作。(*実用上、ソフトスイッチング領域をわずかに逸脱する場合もソフトスイッチングと呼ばれる。)

すなわち、あるスイッチング動作においてそのデバイスの電圧および電流が、下図のように$${v_\mathrm{ds}}$$軸および$${i_\mathrm{ds}}$$軸に沿ったものであればそれをソフトスイッチングと呼ぼうという定義です。

この定義では明らかなハードスイッチング、すなわちオーバーラップ損失が$${\frac{1}{6}v_\mathrm{ds,on}i_\mathrm{ds,off}\frac{t_\mathrm{r}}{T}}$$を超えるようなスイッチングは定義できますが、ZVSやZCSのような動作を定義できません(e.g. ZVSの初期動作では負のドレイン電流、すなわち第四象限での動作が必要です)。

この定義では、オーバーラップ損失を許容する一方で、過渡応答中$${v_\mathrm{ds,on}}$$および$${i_\mathrm{ds,off}}$$を超えてはならないということから、波形のオーバシュートを許容していません。このことから、以下のような指摘もされています。

電気学会の定義はスイッチング損失には甘く、サージ電圧、サージ電流には厳しいと言えるでしょう。

近年ではZVSやZCSといった$${v_\mathrm{ds}-}$$$${i_\mathrm{ds}}$$平面では記述が困難な、より詳細な損失発生のメカニズムと、その損失を低減するアプローチが重要視されています。そこで、ここからはスイッチング損失に焦点を当ててその動作の理解を図ります。

MOSFETのスイッチング損失

はじめに、スイッチング損失と負荷電流の関係についてその概略図を下に示します。

この図は、ハイサイドMOSFETターンオン時の損失発生について定性的に示したものです。スイッチング損失は、負荷電流$${I_\mathrm{sw}}$$の状態によって、ZVS, iZVS, ZCS, そしてhard switchingに分類することができます。そして、これらの状態はスイッチング損失全体に寄与する各損失の構成種類によって決まります。

上に示した各損失はMOSFETの構造と深くかかわりがあるため、損失の説明の前にMOSFETの基本構造とスイッチングのメカニズムについて説明します。

MOSFETの構造と寄生キャパシタンス

MOSFETのの各端子はGate, Source, Drainと呼ばれ、Gate-Source間に電圧が印可されることで酸化膜構造を有するゲートおよびサブストレートに電荷がチャージされ、Drain-Source間にチャネルが形成されてMOSEFTが導通します。

そして、MOSFETは構造上各端子間に寄生容量を有し、各端子の頭文字を取ってGate-Source間キャパシタンス$${C_\mathrm{gs}}$$、 Gate-Drain間キャパシタンス$${C_\mathrm{gd}}$$、そしてDrain-Source間キャパシタンス$${C_\mathrm{ds}}$$が下図のように存在します。

そして、構造とは別にこれら寄生キャパシタが並列動作を行うことでスイッチング動作が行われます。等価回路および計算式上で扱いやすくするため、次の置換が行われます。

$${C_\mathrm{iss}=C_\mathrm{gs}+C_\mathrm{gd}}$$

$${C_\mathrm{oss}=C_\mathrm{ds}+C_\mathrm{gd}}$$

$${C_\mathrm{rss}=C_\mathrm{gd}}$$

これらは順に入力容量、出力容量、帰還容量と呼ばれます。MOSFETの損失はこれら寄生容量と関係します。また、MOSFETを効率よく駆動するために、一般的には$${C_\mathrm{iss},C_\mathrm{oss}>>C_\mathrm{rss}}$$の関係があり、ゲート駆動を安定させるために$${C_\mathrm{iss}}$$はDrain-Source電圧に対して一定である特徴を示します。

続いてここからは、MOSFETで発生する各損失について説明します。

Gate Drive loss

初めに説明するGate Drive lossは、$${C_\mathrm{iss}}$$に関係する損失です。チャネルを形成するためにGateに電荷を蓄積させますが、これはMOSFETの導通に$${C_\mathrm{iss}}$$を充電するエネルギーが必要であることを意味します。

このエネルギー$${E_ \mathrm{GD}}$$は、ゲート電圧$${V_\mathrm{g}}$$によって$${Q_\mathrm{g}}$$の電荷をチャージしたとすると、

$${E_\mathrm{GD}=V_\mathrm{g}Q_\mathrm{g}=V_\mathrm{g}\int_0^{V_\mathrm{g}}C_\mathrm{iss}(v)dv}$$,

として表されます。また、キャパシタンスは面積に比例することと、この充電はスイッチング毎に行われることから、半導体チップエリアの単位面積当たりのGate drive loss $${P_\mathrm{GD}}$$はダイ面積$${A_\mathrm{die}}$$およびスイッチング周波数$${f_\mathrm{sw}}$$を用いて次式であらわされます。

$${P_\mathrm{GD}=A_\mathrm{die}f_\mathrm{sw}V_\mathrm{g}\int_0^{V_\mathrm{g}}C'_\mathrm{iss}(v)dv}$$,

ここで、$${C'_\mathrm{iss}}$$はチップエリア単位面積当たりの入力容量です。この損失はMOSFET駆動に最低限必要なエネルギーであり、どのような動作状態でも必ず必要となります。

Coss discharge loss

次に$${C_\mathrm{oss}}$$の充放電に関係する損失について説明します。この損失の発生は、ZVS動作によって回避可能ですが、それ以外の動作では発生する損失です。

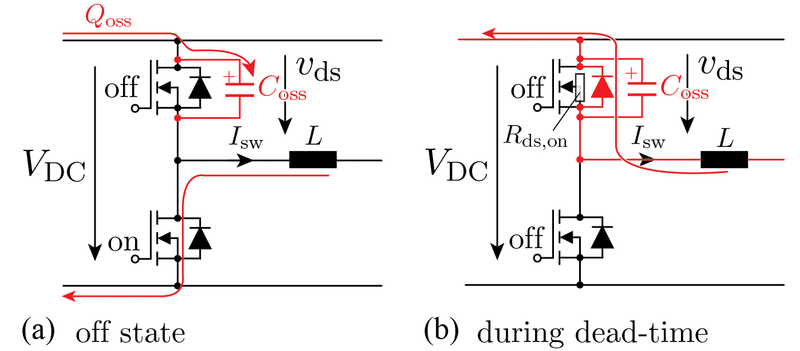

ハイサイドスイッチに着目して、ハイサイドMOSFETがオフ、ローサイドがオンのとき、電源$${V_\mathrm{DC}}$$によってDrain-Source電圧が$${V_\mathrm{DC}}$$と等しくなるまで$${C_\mathrm{oss}}$$が充電されます。

スイッチングノードが解放状態、すなわち$${I_\mathrm{sw}=0}$$ (i.e. ZCS)を仮定すると、ハイサイドMOSFETがターンオンしたのち、$${C_\mathrm{oss}}$$に蓄積された電荷が放電し、MOSFETのDrain-Source間オン抵抗$${R_\mathrm{ds,on}}$$によって放熱されることでMOSFETの電圧が下がっていきます。したがって、先ほどと同様に$${C_\mathrm{oss}}$$の充電に必要なエネルギーが

$${P_\mathrm{oss}=A_\mathrm{die}f_\mathrm{sw}V_\mathrm{ds}\int_0^{V_\mathrm{ds}}C'_\mathrm{oss}(v)dv}$$,

とあらわされます。ここで$${V_\mathrm{ds}}$$はオフ時のDrain-Source間電圧、$${C'_\mathrm{oss}}$$は単位面積当たりの出力容量です。

ZVSによってこの損失を回避するメカニズムを次に示します。ハイサイドMOSFETオフ時には先ほどと同様$${C_\mathrm{oss}}$$に電荷が蓄積されますが、この時誘導性負荷に負の電流を流します。デッドタイムに入ってレグのMOSFETが共にオフ状態になったとき、誘導性負荷に蓄積されたエネルギーが負荷電流に慣性を持たせるので、この負荷電流がボディーダイオードを導通させ、$${C_\mathrm{oss}}$$に蓄積された電荷が放電されます。

この時経路にオン抵抗は含まれないため、$${C_\mathrm{oss}}$$に蓄積された電荷は損失とならずに電源に回生されます。誘導性負荷に蓄積されたエネルギーが不十分だと、$${C_\mathrm{oss}}$$の放電が途中で停止し、残りのエネルギーがオン抵抗で放熱されることになるincomplete ZVS (iZVS)となります。

Overlap loss

最後に、$${C_\mathrm{rss}}$$に関係する損失について説明します。Overlap損失はいわゆる$${P=VI}$$であらわされる損失で、電流の立下りが遅いか、あるいは電圧の立ち上がりが早いことによって電圧・電流の重なりが生じることで発生する損失になります。

下図はハイサイドMOSFETがハードスイッチングでターンオンする際の電圧および電流の変化を示しています。

初めのオフ状態からゲート電圧が増加してターンオンに向かう際の(a)では、Drain-Source間にDC電圧が印可された状態で、ゲートドライブ回路によって$${C_\mathrm{gs}}$$に電荷が蓄積されゲート電圧が上昇します。

次に、ゲート電圧がthreshold電圧を上回ると導通が始まり(b)、$${C_\mathrm{gd}}$$および$${C_\mathrm{ds}}$$に蓄積されていた電荷が放電されることで$${v_\mathrm{ds}}$$が減少します。このとき、ゲートドライブ回路が供給する電力は$${C_\mathrm{gd}}$$の電荷を放電するために使われることになり、ゲート電圧の上昇が止まります。この一定の電圧状態はMirror Plateauとよばれます。Drainを共有していることから$${C_\mathrm{gd}}$$および$${C_\mathrm{ds}}$$の電圧の変化量$${dv/dt}$$は等しく、したがって、より$${C_\mathrm{gd}}$$の容量が少ない、あるいは$${Q_\mathrm{gd}}$$のチャージが速いほど$${v_\mathrm{ds}}$$の減少が早く、Mirror Plateau区間が減少することでOverlap損失の低減が可能です。

最後に$${v_\mathrm{ds}}$$の電圧が完全に0になることで(c)、ターンオンが完了します。この過程で電圧と電流が重なった部分、すなわち$${\int_\mathrm{begin}^\mathrm{end}v_\mathrm{ds}i_\mathrm{ds}dt}$$がOverlap損失で、Mirror Plateau区間の長さに比例することから、

$${P_\mathrm{overlap}=A_\mathrm{die}f_\mathrm{sw}V_\mathrm{ds}I_\mathrm{ds}\frac{Q'_\mathrm{gd}}{I_\mathrm{g}}}$$,

と近似できます。ここで$${Q'_\mathrm{gd}}$$は単位面積当たりの蓄積電荷、$${I_\mathrm{g}}$$はターンオン時の平均ゲート電流です。

ほかにも、寄生ダイオードのReverse Recoveryや導通損が発生しますが、MOSFETそのもので生じる損失は以上になります。

MOSFETの損失とFigure of Merit (FOM)

MOSFETではスイッチング損失のほかに、半導体の導通時に生じるジュール損失として

$${P_\mathrm {joule}=\frac{R'_\mathrm{ds,on}}{A_\mathrm{die}}I^2_\mathrm{RMS},}$$

が存在します。ここで、$${R'_\mathrm{ds,on}}$$は単位面積当たりのオン抵抗を、$${I_\mathrm{RMS}}$$は素子を導通する電流の実効値を表します。

以上より、デバイス単位面積当たりの半導体で生じる損失は以下の式で表すことができます。

$$

\begin{array}{l}

P_\mathrm{semi}(A_\mathrm{die})=\frac{R'_\mathrm{ds,on}}{A_\mathrm{die}}I^2_\mathrm{RMS}+A_\mathrm{die}f_\mathrm{sw}V_\mathrm{g}\int_0^{V_\mathrm{g}}C'_\mathrm{iss}(v)dv \\

\ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ +A_\mathrm{die}f_\mathrm{sw}V_\mathrm{ds}\int_0^{V_\mathrm{ds}}C'_\mathrm{oss}(v)dv+A_\mathrm{die}f_\mathrm{sw}V_\mathrm{ds}I_\mathrm{ds}\frac{Q'_\mathrm{gd}}{I_\mathrm{g}}

\end{array}

$$

半導体製造メーカーはこのチップエリア$${A_\mathrm{die}}$$を最適化、すなわち損失を最小にするよう設計します。すなわち、

$${\frac{\partial P_\mathrm{semi}}{\partial A_\mathrm{die}}=0,}$$

を目指します。この条件を満たすとき、損失の最小値は

$${P_\mathrm{semi,min}(A_\mathrm{die,opt})=2I_\mathrm{RMS}\sqrt{f_\mathrm{sw}R'_\mathrm{ds,on}\left(V_\mathrm{g}\int_0^{V_\mathrm{g}}C'_\mathrm{iss}(v)dv+V_\mathrm{ds}\int_0^{V_\mathrm{ds}}C'_\mathrm{oss}(v)dv+V_\mathrm{ds}I_\mathrm{ds}\frac{Q'_\mathrm{gd}}{I_\mathrm{g}}\right)} \\ \approx 2I_\mathrm{RMS}\sqrt{f_\mathrm{sw}R'_\mathrm{ds,on}\left(V_\mathrm{g}\int_0^{V_\mathrm{g}}C'_\mathrm{iss}(v)dv+V_\mathrm{ds}\int_0^{V_\mathrm{ds}}C'_\mathrm{oss}(v)dv+V_\mathrm{ds}I_\mathrm{ds}\int_0^{V_\mathrm{ds}}C'_\mathrm{rss}(v)dv /I_\mathrm{g}\right)} }$$

となります。

スイッチング損失を表している3つの項の内、どの項が支配的になるかどうかは動作状態に依存しますが、ここでは$${C_\mathrm{rss}}$$が$${C_\mathrm{iss}}$$に含まれていることから、$${C_\mathrm{iss}}$$に着目します。この時半導体の損失は

$${P_\mathrm{semi,min}= 2I_\mathrm{RMS}\sqrt{f_\mathrm{sw}R'_\mathrm{ds,on}\left(V_\mathrm{g}\int_0^{V_\mathrm{g}}C'_\mathrm{iss}(v)dv\right)}\approx 2V_\mathrm{g}I_\mathrm{RMS}\sqrt{f_\mathrm{sw}R'_\mathrm{ds,on}C'_\mathrm{iss}}}$$

とあらわされます。この式は、半導体で生じる損失を最適化する際に$${f_\mathrm{sw}R'_\mathrm{ds,on}C'_\mathrm{iss}}$$のパラメータのすべてを同時には増加させられないトレードオフが存在することを意味しています。すなわち、ある半導体を一定損失の下で高周波$${f_\mathrm{sw}}$$で駆動できるかどうかは、

$${f_\mathrm{sw}=\frac{1}{R'_\mathrm{ds,on}C'_\mathrm{iss}}}$$

を満たせるかによって決まるということです。この指標が、今日でもワイドバンドギャップ半導体の性能指標として用いられるBaliga High Frequency Figure of Merit (BHFOM, バリガの性能指標)です。

まとめ

半導体、特にPower MOSFETで生じる損失について説明しました。学部の授業では電子回路、パワーエレクトロニクスといった授業でMOSFETの駆動手法や特性は教わりましたが、ソフトスイッチングに関しては全く分からず、研究室でもその理解は曖昧なままでした。ソフトスイッチングはスイッチング損失を低減する技術ですが、発生する損失のある1つを低減できてもほかの損失が悪化するトレードオフが存在します。このことが、理解を難しくしている要因だと思っています。

今回は各損失のメカニズムについて説明しましたが、ソフトスイッチング技術のトレードオフ関係には至っていないので、また知見が溜まったら追記しようと思います。

この記事が気に入ったらサポートをしてみませんか?