デバイス・ツリーを読む 続き

https://github.com/Xilinx/qemu-devicetrees/blob/master/include/versal/rpu.dtsh にある設定値の意味

arm,tcmtr=<0x00010001>;

おそらくTCM Type Register。Tightly Coupled Memory(TCM)のうち、ATCMとBTCM 1つずつ備えていることを示している。

Xilinx QEMUのtarget/arm/cpu_tcg.cに以下のコメントがある。ただしこれはCortex-R52用の設定。

/* Has TCM A, B & C. */

cpu->tcmtr = 0x80000007;arm,ctr=<0x8003c003>; \

Cache Type Registerのこと。Cortex-R5 TRM Revision: r1p2曰く

[31:28]: Reservedで1000(=8)固定

[27:24]: Cache Writeback Granule。0だとno informationとのこと。

[23:20]: Exclusives Reservation Granule。0だとno informationとのこと

[19:16]: DMinLine。log2(M), M=データキャッシュラインサイズ。3なので8ワード。

[15:14]: 3固定。

[13: 4]: 0固定

[3: 0]: IMinLine。DMinLineの命令キャッシュ版。3なので8ワード

arm,clidr=<0x09200003>; \

Cache Level ID Register。実装されてるキャッシュレベルを示す。

[29:27]: Level of Unification。1なので、level 2であり、D$かI$があることを示す。

[26:24]: Level of Coherency。1なので、level 2であり、D$かI$があることを示す。Level of Unificationと同じ説明が書いてあるので誤植かと思ったが、ARMv8A(https://developer.arm.com/documentation/ddi0595/2021-12/AArch64-Registers/CLIDR-EL1--Cache-Level-ID-Register?lang=en#fieldset_0-26_24)を見てもそう書いてあり、ただし使われ方が異なるようである。

[23:21]: Level of Unification Inner Shareable: 1なので、level 2。

[1]: D$がある

[0]: I$がある

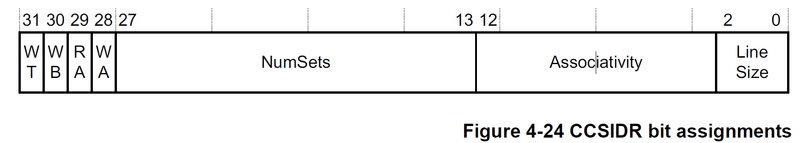

arm,ccsidr0 = <0xf01fe019>; \

Cache Size ID Register。

WT:Write Throughのサポート可

WB: Write Backのサポート可

RA: Read Allocationのサポート可。Read Allocationとは、リードのキャッシュミスでのみキャッシュラインに主記憶からのデータを残すこと。

WA: Write Allocationのサポート可。リードとライトの両方のキャッシュミスでキャッシュラインに主記憶からのデータを残す。

NumSets: セット数。+1した数が実際の値。11111111=255になってるので256エントリのキャッシュ。

Associativity: ウェイ数。+1した数が実際の値。11=3になってるので4way。

Line Size: 0の時4 words。1の時8 words。1なので8 words/cache line。

32KB キャッシュであることを示してる。

arm,ccsidr1の方も同じ値だが、2つあるのはD$とI$の分なのだろうか?

arm,mp-affinity = <glue(glue(0x,c), 0 ## i)>; \

Multiprocessor Affinity Register(MPIDR)か?

[31:30]: マルチプロセシング拡張, 00は拡張なし。

[15:8]: Affinity Level1, システム中のプロセッサグループ。

[7:0]: Affinity Level0, あるグループ中のCPU。

arm,id_pfr0 = <0x131>; \

The Processor Feature Register 0。実行状態サポートとプロセッサのプログラマモデルに関する情報を提供する。

[15:12] State3, ThumbEEサポート, 00はサポートしないことを示す。

[11:8] State2, 実行環境アクセラレーションのサポート, 001はサポートをすることを示す。

[7:4] State1, Thumbエンコーディング, 0x3は全Thumb命令のThumbエンコーディングをサポートすることを示す

[3:0] State0, ARM命令セット, 0x1はARM命令をサポートすることを示す。

arm,reset-hivecs = <1>; \

SCTLR.Vの例外ベクタのアドレス設定をのHIVECSにするかどうかか?

通常は0x00000000-0x0000001C, HIVECSならば0xFFFF0000-0xFFFF001C.

(おまけ) Zynq MPの方 https://github.com/Xilinx/qemu-devicetrees/blob/xilinx-v2020.1/zynqmp-arm.dtsi にもRPU用の設定値があり、そちらにしかない設定について。

arm,midr=<0x411fc153>; \

Main ID Register。

[31:24], Implementer, 0x41はARM Limited。

[23:20], Variant(Major Revision of Processor), 0x1はrevision 1。

[19:16], Architecture Version, 0xfはfeatureレジスタ参照の意味。

[15:4], Processor Part Number, 0xc15はCortex-R5の意味。

[3:0], (Minor) Revision, 0x3なので、[23:20]と合わせてr1p3の意味。

この記事が気に入ったらサポートをしてみませんか?