【注目ニュース】KIOXIA 界面層へのメタル添加により電荷トラップと分極を制御した高サイクル耐性FeFETを開発

発表日:2024年4月9日

概要

KIOXIA(旧東芝メモリ)は、トランジスタのゲート絶縁体に強誘電体HfOを利用したFeFETにおいて、界面層にメタルと窒素を添加したTrap controlled interfacial layer(TCIL)を導入することでサイクル耐性を改善しました。

以下にKIOXIAの公式HPの発表を引用します。

トランジスタのゲート絶縁体に強誘電体HfOを利用したFeFETは高速かつ低い書込/消去電圧で駆動が可能で、SCM、ファイルメモリなどの幅広い領域のメモリ候補として期待されています。FeFETの課題の一つはサイクル耐性の改善です。

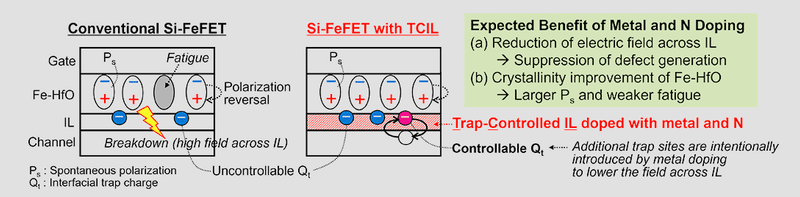

図1は今回提案したサイクル耐性改善に向けたコンセプトです。シリコンをチャネル材料として利用したFeFETではHfOベースの強誘電体材料とチャネルの間に低誘電率のSiOが形成されます(図1.IL)。

この界面SiOは書込/消去時に高い電界が印加されることで劣化し、FeFETの特性に悪影響を及ぼします。

本論文では、強誘電体の改質と界面層の劣化抑制を実現するため、界面層にメタルと窒素を添加したTrap controlled interfacial layer(TCIL)を導入しました。TCILは書込/消去時に電荷をトラップし、界面層の電界を抑制することでサイクル後のFeFET特性を改善できると期待されます。

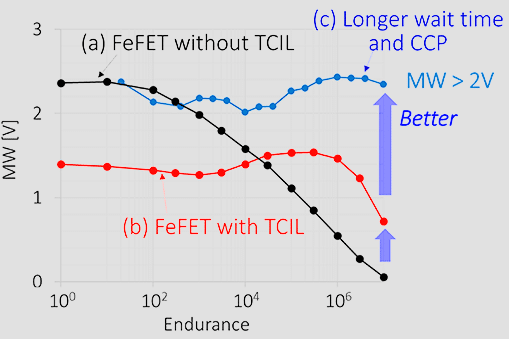

TCILを利用したFeFETのメモリ特性(図2(b))は、メタル添加していないFeFET(図2(a))と比較して初期のメモリウインドウ(MW)が減少するものの、サイクル後のMWが改善します。初期MWの減少は分極反転電荷Psをキャンセルする過剰なトラップ電荷Qtが界面へのメタル添加により増大したためです。

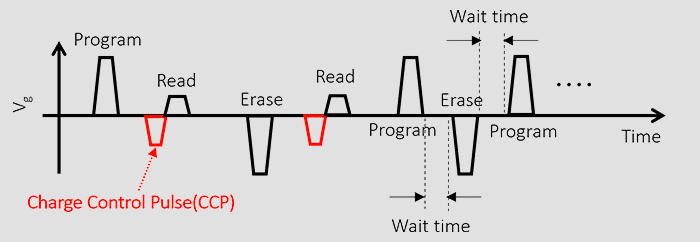

次に、図3に示す界面のQtを調整するチャージ制御パルス(CCP)を読出前に追加してMWを拡大する動作方法を採用しました。Qtの増大を抑制する動作方法と界面へのメタル添加を組み合わせることで、107回後にMW>2Vを達成しました(図2(c))。チャージ制御したFeFETは、サイクル耐性とMWの両方を改善でき様々なメモリアプリケーションに適用できると考えています。

解説

どのような製品でも避けられないのが経年劣化の問題です。初期においては高い特性を出していてもそれが時間経過とともに、低下していくことはある程度避けられませんが、Sustainableな社会を実現するためには、できるだけ長寿命にする必要があります。

分かりやすい例で言えば、購入時は最高速度150 km/hでも、1年後に最大50 km/hになる車はSustainableではありません。それならずっと最大100 km/hが維持される方がサイクル耐性が高いという意味でよい車になります。

この発表では、界面においてサイクル耐性を低減する低誘電体層の形成を金属を入れることにより(この金属の種類は明らかにされていない?)阻害することに成功したとのことでした。

界面あるところに欠陥あり

太陽電池もそうですが、界面を制するものは性能向上を制すると言えそうです。これからも界面制御には技術的なブレイクスルーが多く隠されていそうです。

それでは!

参考文献

界面層へのメタル添加により電荷トラップと分極を制御した高サイクル耐性FeFET | KIOXIA - Japan (日本語)

[1] K. Suzuki et al., “High-Endurance FeFET with Metal-Doped Interfacial Layer for Controlled Charge Trapping and Stabilized Polarization”, IEDM, 35-5 (2023).

よろしければサポートもよろしくお願いいたします.頂いたサポートは主に今後の書評執筆用のために使わせていただきます!