チップレット信頼性の未来

100%のレーンカバレッジで配線不良を予測

チップメーカーは、トランジスタ密度を高めることなくシリコン製造のレチクルサイズの限界を克服するため、先進的なパッケージングにますます注目している。この方法は、サイズとともに指数関数的に減少する歩留まりを改善しながら、異なるプロセス・ノードのダイとのハイブリッド・デバイスも可能にします。

しかし、2.5D/3D設計は、インターコネクトの見通しが悪いという最も重要な課題の1つである。

ダイ・ツー・ダイ(D2D)インターコネクトの見通しの悪さがもたらす犠牲

エンジニアはチップレットの設計に何ヶ月も費やしますが、テスト・プログラムからアクセスできる内部ダイ・ピンがほとんどないことが判明します。個々のダイが徹底的なテストを受けたとしても、先進的なパッケージでそれらを接続する多数のレーンは、しばしば闇に葬られます。

DFT BISTに基づく従来のテスト方法は、エンジニアに限られた救済しかもたらさない。テスト・モードにおいてのみ有効であり、実際のシナリオで何が起こるかについては大きな疑問符が残る。また、サンプル・レーンしかカバーしていないため、重要な誤動作を見落とす可能性がある。

そのため、SiP(システム・イン・パッケージ)でダイを組み立てる際、さまざまなD2D配線の欠陥が検出されない可能性がある:

・はんだマイクロバンプ:ボイド、クラック、ボールの欠落

・TSVの問題:クラックやドリル穴の部分的充填

・レーントレースの問題:残留材料によるブリッジショート

もしエンジニアがミッションモードで100%のレーンカバレッジを持っていたらどうなるか

前述したように、一般的なプラクティスでは、テストモードでのみサンプルレーン・カバレッジを提供している。

一方、100%のレーンカバレッジがあれば、品質リスクを回避することができる。そして、テストがミッションモードで実行できれば、それは信頼性の聖杯となる。エンジニアは、たとえ何千もの欠陥があったとしても、すべてのレーンにおいて実際の条件下で欠陥を検出できるようになる。

このレベルのカバレッジは、インターコネクトがフィールドで問題なく動作するという完全な確信をもたらします。

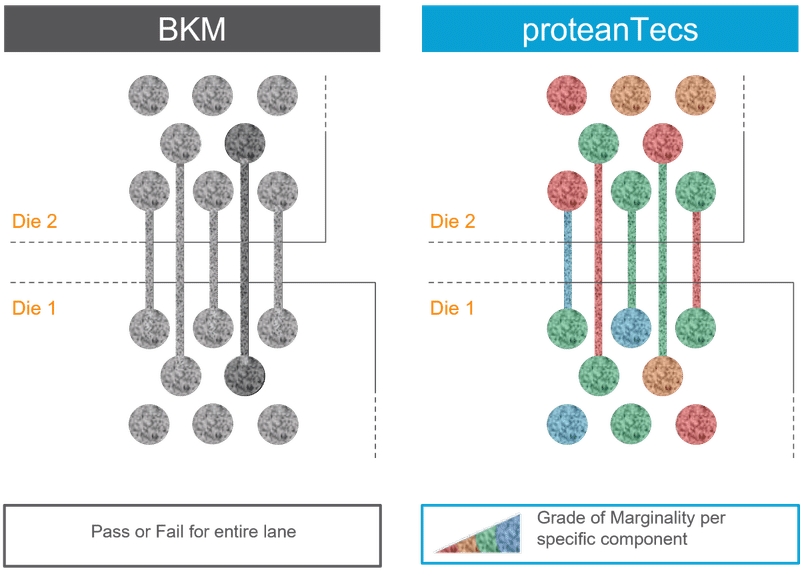

パラメトリックレーングレーディングによるインターコネクト故障予測

一般的な試験方法のもう一つの欠点は、出力が白か黒かであることです。この方法では、レーンが合格か不合格かを示すだけで、性能が限界に達している場合により微妙な予知は得られません。このアプローチは、劣化が早い傾向のある性能の低いレーンが最終製品に混入し、早期故障につながる場合に問題となる。

対照的に、パラメトリックレーンのグレーディングは単なる合格/不合格のテストを超えます。レーンごとのマージナリティの評価を提供します。この詳細さにより、現在テストが合格している場合でも、予備のレーンとの交換のためのパフォーマンスの閾値を設定することが可能です。また、製造ラインでの収量向上や品質・安全性の向上、さらにはフィールドでの寿命延長を実現します。

proteanTecs D2D相互接続モニタリングソリューション

proteanTecsでは、ミッションモードの100%レーンカバレッジとパラメトリックレーングレーディングを組み合わせ、両方の長所を提供します:

・多数のレーンそれぞれに何が起きているかを正確に把握

・テストモードでもミッションモードでも、実際の条件下で実行可能

・チップの故障時期を予測し、故障が発生する前に劣化したレーンを交換

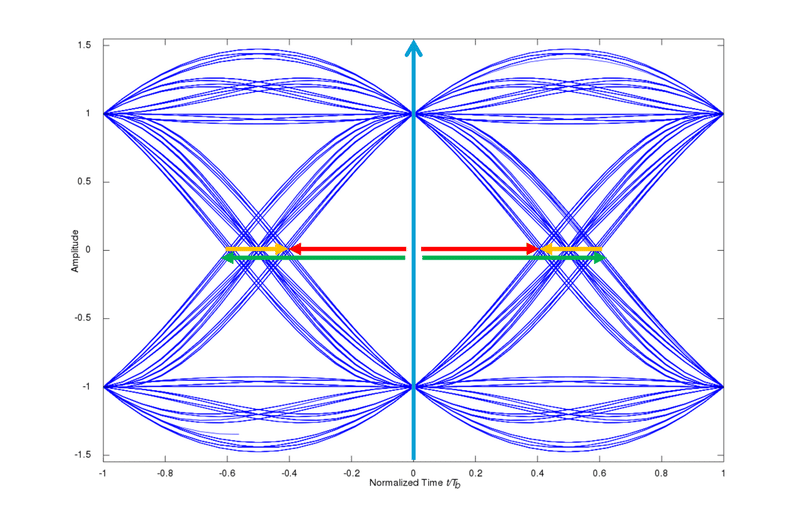

専用のproteanTecsエージェントIPが設計に統合されているため、空のバンプ・アレイ・シリコンを使用して面積のペナルティなしに完全なレーンカバレッジが可能です。これらのエージェントの測定値は、データ分析プラットフォームに送信され、いくつかのパラメータに基づいて各レーンを評価し、早期の故障予測を可能にします:

・最大アイ幅測定(下の緑の矢印)

・最小アイ幅測定(下の赤い矢印)

・アイ幅交差ジッター、最大-最小(下のオレンジの矢印)

・対称性解析のため、アイの右側(データからクロック)と左側(クロックからデータ)を別々に測定

・測定は、各クロック位相(通常、DDRの場合は2つ、QDRの場合は4つ)について別々に行われます。

ここでは、クロック位相の1つについて、アイ・ダイアグラムと測定結果を示します。これらの測定は、新製品導入(NPI)時に、最初のチップが到着したときに、さまざまなプロセス、電圧、温度の下でレーン性能を特性評価するのに有用です。

量産時には、アセンブルされたユニットの異常値を検出することで、チップ全体を廃棄する代わりに、欠陥のあるレーンや弱いレーンを予備のレーンと交換することで歩留まりを向上させることができます。

最後に、現場においては、レーンの劣化を検出することで、故障が発生する前に予備レーンに積極的に交換したり、予備レーンがなくなったらモジュールを交換したりすることで、予知保全が可能になります。

結論として、ProteanTecsの100%カバレッジ・パラメトリック・レーン・グレーディング・インミスオンモードは、ヘテロジニアス・インテグレーション・テストにおける最も重要な課題の1つである、インターコネクトの視認性の低さ に対処しています。チップレットの品質、信頼性、安全性を高め、スペアレーンやレーン修復と組み合わせることで、歩留まりを向上させます。

proteanTecsのD2Dソリューションは、HBM3やUCIeを含む幅広いインターフェースと基板をサポートしています。

チップレット信頼性の未来からどのような恩恵を受けられるか、お知りになりたいですか?ホワイトペーパーをダウンロードするか、こちらからお問い合わせください。